winjer

Member

Intel Confirms Development of 3D-Stacked Cache Technology for Processors

At the InnovatiON 2023 Day 1 Q&A, Intel CEO Pat Gelsinger discussed the company's ongoing work in 3D-stacked cache technology for their processors. The technique involves expanding the on-die last-level cache (L3 cache) by stacking an additional SRAM die atop the current cache, integrating it...

At the InnovatiON 2023 Day 1 Q&A, Intel CEO Pat Gelsinger discussed the company's ongoing work in 3D-stacked cache technology for their processors. The technique involves expanding the on-die last-level cache (L3 cache) by stacking an additional SRAM die atop the current cache, integrating it with the cache's high-bandwidth data fabric.

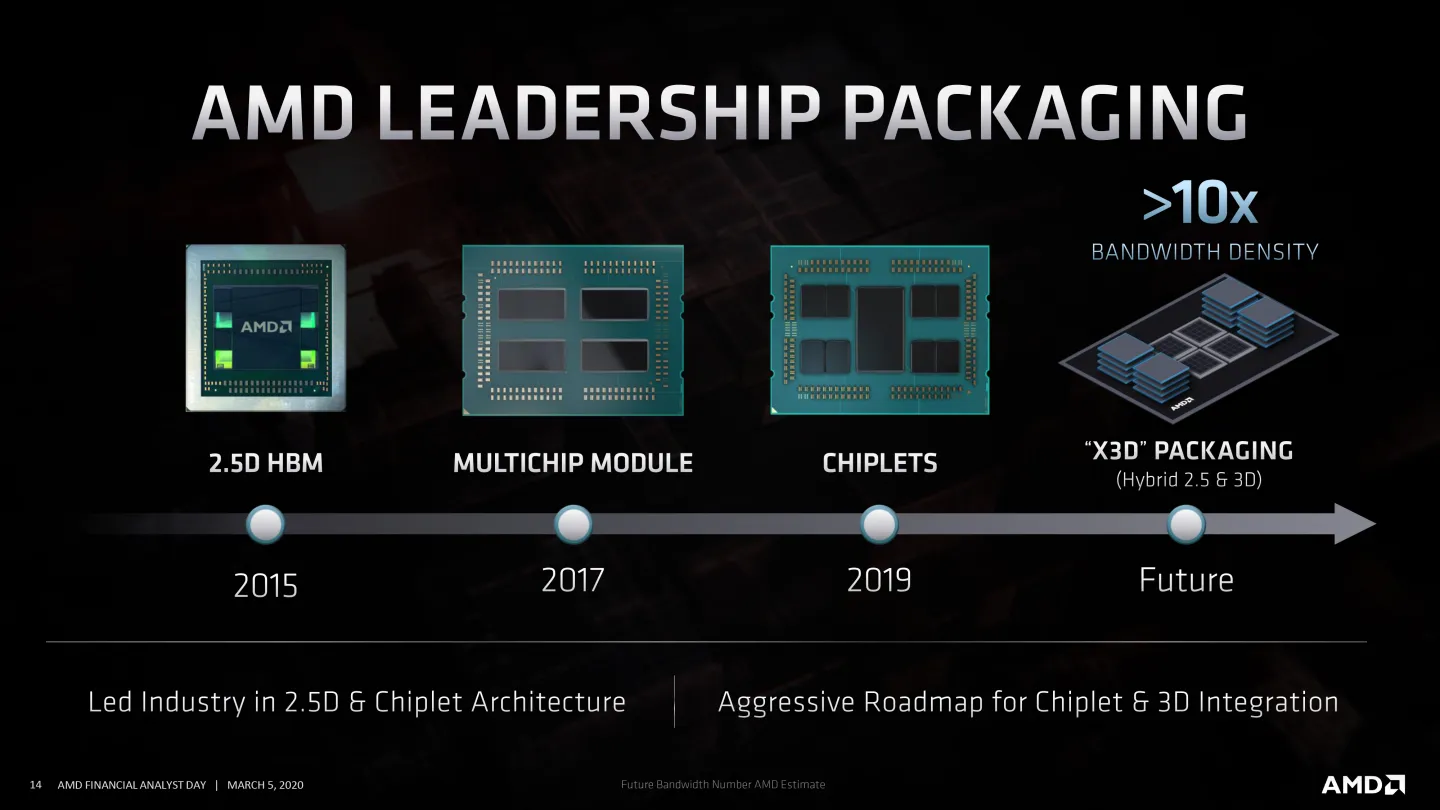

Interestingly, the stacked cache operates at the same velocity as the on-die cache, offering a continuous addressable cache memory block. Although this technology is not slated for the Meteor Lake, Intel plans its implementation in various future processors. AMD has already integrated 3D-stacked cache technology into its processors, yielding significant results. In client processors, such as the Ryzen X3D series, the augmented cache notably enhances gaming performance by enabling the CPU cores to swiftly access more rendering data. For server processors, models like EPYC "Milan-X" and "Genoa-X" have seen marked performance boosts in memory-heavy computational tasks, attributed to the increased cache.

Gelsinger said Intel plans to connect chip dies vertically using its EMIB and Foveros processes, "so we feel very good that we have advanced capabilities for next-generation memory architectures." He added that the technology will be used in Intel's own products and also be available to Foundry (IFS) customers.

3D cache was a great success for AMD, both for gaming CPUs and for servers. So it was to expect other companies would copy AMD's technology.

Still, no word on when it will be available, only that it's being developed.